# A Miniaturized MMIC Analog Phase Shifter Using Two Quarter-Wave-Length Transmission Lines

Hitoshi Hayashi, *Member, IEEE*, Tadao Nakagawa, *Member, IEEE*, and Katsuhiko Araki

**Abstract**—This paper describes a miniaturized monolithic-microwave integrated-circuit (MMIC) analog phase shifter using two quarter-wave-length transmission lines. A conventional analog phase shifter employs an analog phase-shifter topology using a 3-dB 90° branch-line hybrid requiring four quarter-wave-length transmission lines. Thus, in the first stage of our study, we present a new analog phase-shifter topology using only two quarter-wave-length transmission lines. The phase shifter here has only one-half as many transmission lines as a conventional analog phase shifter using a 3-dB 90° branch-line hybrid, and the circuit can be miniaturized to less than one-fourth as compared to the conventional analog phase shifter. Furthermore, we show that the operating frequency range of the phase shifter is very wide and can obtain large phase variation with small capacitance variation. Next, an experimental Ku-band MMIC analog phase shifter is presented. A phase shift of more than 180° and an insertion loss of  $3.6 \pm 1.1$  dB are obtained at the frequency range from 12 to 14 GHz. The chip size of the experimental MMIC phase shifter is less than 3.0 mm<sup>2</sup>.

**Index Terms**—Analog circuits, MESFETs, MMIC phase shifters.

## I. INTRODUCTION

RECENTLY, with the advent of monolithic-microwave integrated-circuit (MMIC) technology, so-called “active integrated antennas,” in which oscillators, phase shifters, low-noise amplifiers, power amplifiers, and antennas are compactly integrated, have been proposed to facilitate the miniaturization of wireless communication devices [1]–[4]. An analog varactor-diode phase shifter, which is composed of a 3-dB 90° hybrid and two varactor diodes, can change the phase continuously by varying the biases of the varactor diodes [5]. Since it is possible to obtain any number of phase states, it is thought that the applicable range of the analog phase shifter is wider than that of a digital phase shifter. In order to miniaturize the MMIC analog varactor-diode phase shifter, a small-sized 90° hybrid must be developed. Commonly used branch-line 90° hybrids are composed of straight quarter-wave-length transmission lines. Gupta *et al.* have proposed a configuration of a quasi-lumped-element branch-line 90° hybrid, which uses an inductor–capacitor  $\pi$ -network in place of distributed-transmission lines [6]. The chip area was reduced successfully to less than 20% of that of the corresponding distributed element design. This technique has reduced the size of the 90° hybrid considerably.

Another approach to miniaturizing the analog phase shifter is to adopt a circuit configuration in which the 90° hybrid is not

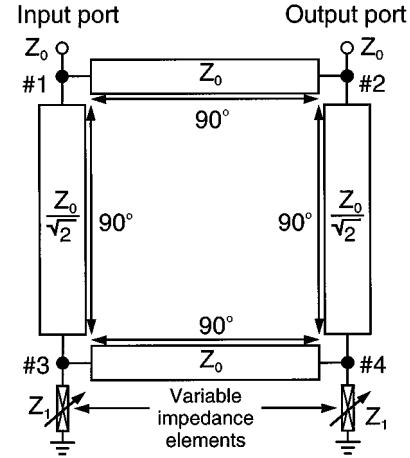

Fig. 1. Conventional analog phase-shifter topology using 90° branch-line hybrid.

needed. We have proposed a novel analog phase-shifter configuration that uses two quarter-wave-length transmission lines [7]. In [7], we analyzed only the case of using two capacitors and/or two inductors as the variable reactance circuits in order to obtain phase-shifter characteristics. In this paper, we will introduce the generalized form of the miniaturized analog phase-shifter topology using two quarter-wave-length transmission lines and describe the experimental results of our MMIC analog phase shifter.

## II. DESIGN APPROACH

### A. Conventional Analog Phase-Shifter Topology

First, we will give an overview of the operating principle of the conventional analog phase-shifter topology using a 90° branch-line hybrid. Fig. 1 shows a conventional analog phase-shifter topology using a 90° branch-line hybrid. The input and output impedances are  $Z_0$ . It is composed of four transmission lines, the characteristic impedance of which is  $Z_0$  and the electrical length of which is 90° at the normalized frequency of  $f_0$ , and two variable impedance elements, the impedances of which are both  $Z_1$ . The 90° branch-line hybrid divides the input signal from port #1 equally between the two output ports, i.e., ports #3 and #4, but with a difference of 90°. Ports #3 and #4 are terminated with identical variable impedance elements. Signals reflected back from ports #3 and #4 are added together at port #2 and no signal returns to port #1. In this case, if the variable reactance elements  $jX_1$  are used as the variable impedance elements  $Z_1$ , this circuit functions as an analog phase shifter with a constant amplitude, and the phase shift  $\theta$ , when the values

Manuscript received August 28, 2000.

The authors are with NTT Network Innovation Laboratories, NTT Corporation, Yokosuka-shi 239-0847, Japan (e-mail: hayashi@wslab.ntt.co.jp)

Publisher Item Identifier S 0018-9480(02)00024-8.

Fig. 2. Simulated frequency characteristics of conventional analog phase shifter for different values of  $C_1$ .  $C_1$  was varied between 0.01, 0.05, 0.1, 0.15, 0.2, 0.25, 0.3, and 0.35 pF. (a) Amplitude variations of  $S_{21}$  and  $S_{11}$ . (b) Phase variation of  $S_{21}$ .

of the variable reactance elements are changed from  $jX_1$  to  $j(X_1 + \Delta X_1)$  at the normalized frequency of  $f_0$ , is expressed by the following equation:

$$\theta = -2 \tan^{-1} \left( \frac{X_1 + \Delta X_1}{Z_0} \right) + 2 \tan^{-1} \left( \frac{X_1}{Z_0} \right) \text{ rad.} \quad (1)$$

Next, we simulated the frequency characteristics of the conventional phase shifter using variable capacitors  $1/(j\omega C_1)$  as the variable reactance elements  $jX_1$  in order to check the validity of the operating principle described above. The simulated frequency characteristics of the conventional analog phase shifter for different values of capacitance  $C_1$  are shown in Fig. 2. Fig. 2(a) shows the amplitude variations of  $S_{21}$  and  $S_{11}$ , and Fig. 2(b) shows the phase variation of  $S_{21}$ . The normalized frequency  $f_0$  is 10 GHz and the normalized impedance  $Z_0$  is 50  $\Omega$ .  $C_1$  is varied from 0.01 to 0.35 pF. In the simulation, we assume that the quarter-wave-length transmission lines have no electrical losses. At the normalized frequency  $f_0$ , we can obtain phase shift of more than 90°. The frequency range, in which  $S_{11}$  is less than -10 dB is only from 9 to 11 GHz. This shows that the operating frequency range of the conventional phase shifter is very narrow. Furthermore, it is difficult to attain miniaturization because we must use four quarter-wave-length transmission lines. If the necessary number of transmission lines can be reduced, we can easily attain miniaturization.

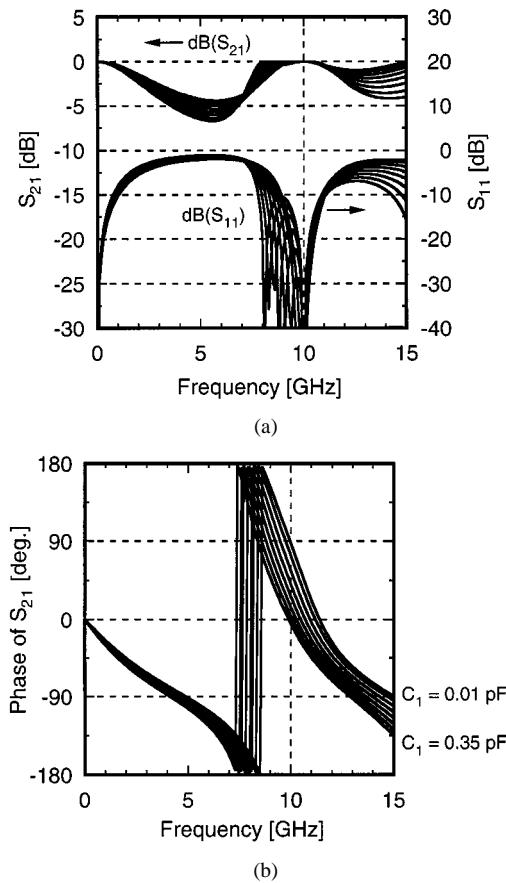

Fig. 3. Novel analog phase-shifter topology using two quarter-wave-length transmission lines.

### B. Novel Analog Phase-Shifter Topology

In order to solve the problems mentioned above, we propose a novel analog phase-shifter topology using two quarter-wave-length transmission lines shown in Fig. 3. The input and output impedances are  $Z_0$ . It is composed of two transmission lines, the characteristic impedance of which is  $Z_2$  and the electrical length of which is 90° at the normalized frequency of  $f_0$ , and two variable impedance elements, the impedances of which are  $Z_1$  and  $Z_3$ , respectively. The reflection coefficients  $S_{11}$  and  $S_{22}$  of this topology at the normalized frequency of  $f_0$  are expressed by the following equation:

$$S_{11} = S_{22} = \frac{\frac{Z_2^2}{4Z_0^2}Z_1 - Z_3}{\frac{Z_2^2}{4Z_0^2}Z_1 + Z_3 + \frac{Z_1Z_3 + Z_2^2}{2Z_0}}. \quad (2)$$

Thus, we can obtain the input-output matching condition at the normalized frequency of  $f_0$  by setting the value of  $Z_3$  and  $Z_1$  as shown in the following equation:

$$Z_3 = \frac{Z_2^2}{4Z_0^2}Z_1. \quad (3)$$

In this case, the reflection coefficients  $S_{11}$  and  $S_{22}$  and the transmission coefficients  $S_{21}$  and  $S_{12}$  of this topology at the normalized frequency of  $f_0$  are expressed by the following equations:

$$S_{11} = S_{22} = 0$$

$$S_{21} = S_{12} = \frac{2Z_0 - Z_1}{2Z_0 + Z_1}. \quad (4)$$

In this case, if the variable reactance element  $jX_1$  is used as the variable impedance element  $Z_1$  and the variable reactance element  $jX_3$  is used as the variable impedance element  $Z_3$ , this circuit functions as an analog phase shifter with a constant amplitude, and the phase shift  $\theta$ , when the values of the variable reactance elements are changed from  $jX_1$  to  $j(X_1 + \Delta X_1)$  at the normalized frequency of  $f_0$ , is expressed by the following equation:

$$\theta = -2 \tan^{-1} \left( \frac{X_1 + \Delta X_1}{2Z_0} \right) + 2 \tan^{-1} \left( \frac{X_1}{2Z_0} \right) \text{ rad.} \quad (5)$$

Since this circuit topology needs only two transmission lines, the circuit can be miniaturized to less than one-fourth as compared with the conventional analog phase-shifter topology.

Next, we simulated the frequency characteristics of the novel phase shifter using the variable capacitor  $1/(j\omega C_1)$  as the variable reactance element  $jX_1$ , and the variable capacitor  $1/(j\omega C_3)$  as the variable reactance element  $jX_3$ , in order to check the validity of the operating principle described above. The simulated frequency characteristics of the novel analog phase shifter for different values of capacitance  $C_1$  are shown in Fig. 4. In this case,  $Z_2$  is set to  $Z_0$  and  $C_3$  is set to four times

Fig. 4. Simulated frequency characteristics of novel analog phase shifter for different values of  $C_1$ .  $C_1$  was varied between 0.01, 0.05, 0.1, 0.15, and 0.2 pF. (a) Amplitude variations of  $S_{21}$  and  $S_{11}$ . (b) Phase variation of  $S_{21}$ .

$C_1$ . Fig. 4(a) shows the amplitude variations of  $S_{21}$  and  $S_{11}$ , and Fig. 4(b) shows the phase variation of  $S_{21}$ . The normalized frequency  $f_0$  is 10 GHz and the normalized impedance  $Z_0$  is  $50 \Omega$ .  $C_1$  is varied from 0.01 to 0.2 pF. In the simulation, we assume that the quarter-wave-length transmission lines have no electrical losses. At the normalized frequency  $f_0$ , we can obtain phase shift of more than  $90^\circ$ . The frequency range, in which  $S_{11}$  is less than  $-18$  dB is from 6 to 11 GHz. This shows that the operating frequency range of the novel phase shifter is more than two times wider than the conventional phase-shifter characteristics shown in Fig. 2. It also demonstrates that we can obtain large phase variation with small capacitance variation.

### III. Ku-BAND MMIC ANALOG PHASE-SHIFTER PERFORMANCE

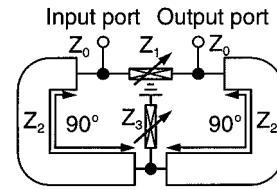

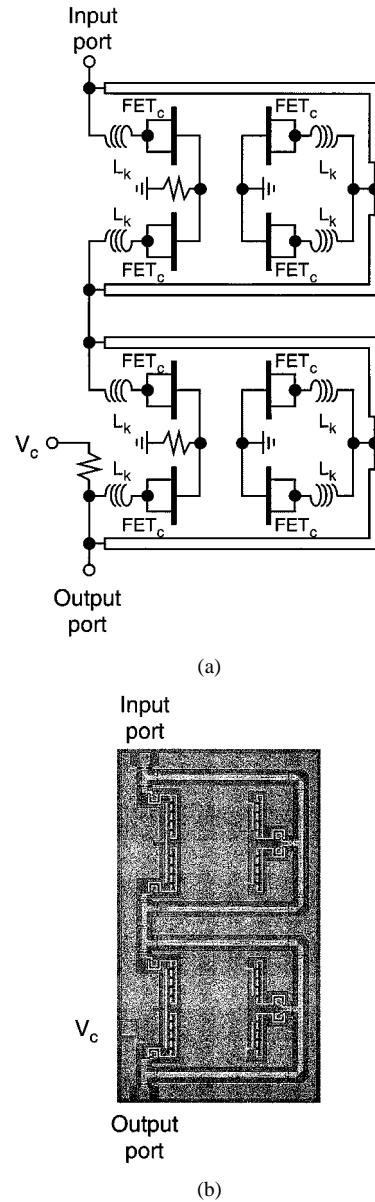

In order to verify the feasibility of using this circuit topology, we fabricated an experimental  $Ku$ -band MMIC analog phase shifter by using a  $0.3\text{-}\mu\text{m}$ -gate-length GaAs MESFET process. Typical values of the transconductance  $g_m$  and cutoff frequency  $f_T$  of the GaAs MESFET were more than  $200 \text{ mS/mm}$  and  $20 \text{ GHz}$ , respectively [8]. Fig. 5(a) shows the circuit configuration. In order to obtain a large phase shift, two components of the phase-shifter circuits were cascade-connected and fabricated into one chip. In this phase shifter, the Shottky-barrier gate capacitance of the GaAs MESFET was used as the capacitance of the varactor diode  $\text{FET}_c$ , by connecting the drain to

Fig. 5. Circuit configuration and chip photograph of experimental  $Ku$ -band MMIC analog phase shifter. (a) Circuit configuration. (b) Chip photograph. The chip size is  $1.28 \text{ mm} \times 2.28 \text{ mm}$ .

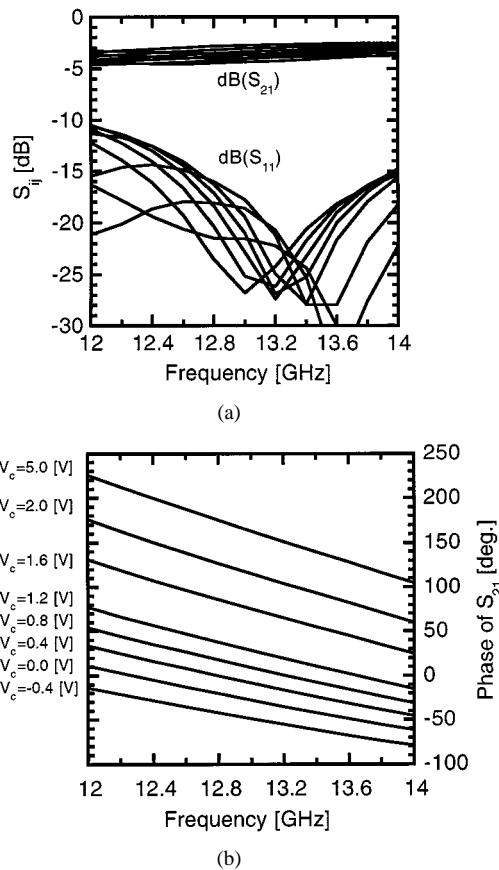

the source of the GaAs MESFET. The gatewidth of the varactor diode is  $200 \mu\text{m}$ . The capacitance variation of the varactor diode at 12 GHz is from 0.25 to 0.6 pF at the reverse-bias voltage from  $-5.0$  to  $0.0$  V. As the figure shows, two serial circuits, each comprising an inductor  $L_k$  and an  $\text{FET}_c$ , are serially inserted between the ports. The inductance value of  $L_k$  is  $0.2 \text{ nH}$ . In addition, two other serial circuits comprising an  $L_k$  and an  $\text{FET}_c$  are connected in parallel to the connection point of the transmission lines. These ensure layout pattern symmetry. Fig. 5(b) shows a chip photograph. This MMIC structure uses “uniplanar” techniques based on the coplanar waveguide [9]. The chip size is  $1.28 \text{ mm} \times 2.28 \text{ mm}$ , which corresponds to an area of less than  $3.0 \text{ mm}^2$ . Fig. 6 shows the measured results of the amplitude variations of  $S_{11}$  and  $S_{21}$ , and the phase variation of  $S_{21}$ . Control voltage  $V_c$  was varied from  $5.0$  to  $-0.4$  V. A phase shift of more than  $180^\circ$  and an insertion loss of  $3.6 \pm 1.1 \text{ dB}$  were

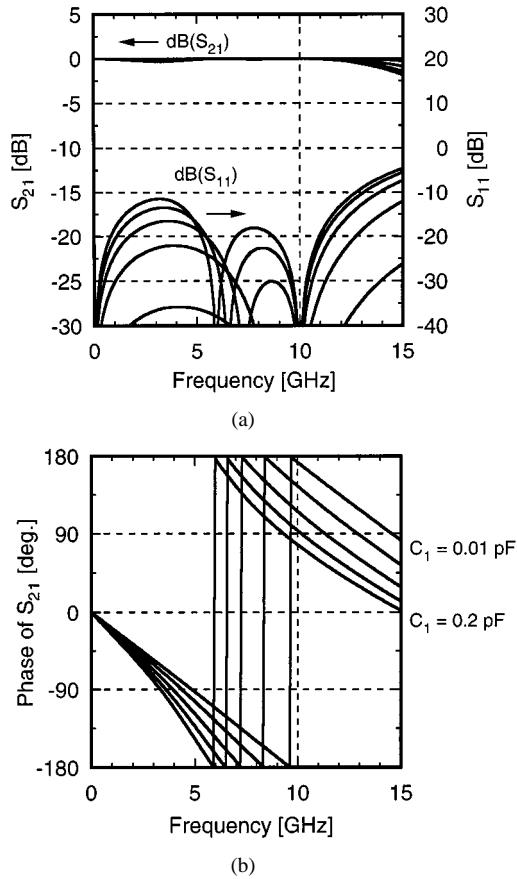

Fig. 6. Measured frequency characteristics of experimental *Ku*-band MMIC analog phase shifter.  $V_c$  was varied between 5.0, 2.0, 1.6, 1.2, 0.8, 0.4, 0.0, and -0.4 V. (a) Amplitude variations of  $S_{21}$  and  $S_{11}$ . (b) Phase variation of  $S_{21}$ .

obtained from 12 to 14 GHz. Intermodulation distortion characteristics at each step were measured by inputting two signals with frequencies of 12 and 12.001 GHz. When the input power levels of both signals were 5 dBm, the relative output level of the desired signal compared with the third-order intermodulation distortion was between 21–44 dB.

#### IV. CONCLUSION

We have presented an analog phase shifter using two quarter-wave-length transmission lines. A conventional analog phase shifter employs an analog phase shifter topology using a 3-dB 90° branch-line hybrid requiring four quarter-wave-length transmission lines, and its size is unsatisfactorily large. Thus, in the first stage of our study, we developed a new analog phase-shifter topology using only two quarter-wave-length transmission lines. The phase shifter here has only one-half as many transmission lines as a conventional analog phase shifter using a 3-dB 90° branch-line hybrid, and the circuit can be miniaturized to less than one-fourth as compared to the conventional analog phase shifter. Furthermore, we showed that the operating frequency range of the phase shifter was very wide and could obtain large phase variation with small capacitance variation. Next, we fabricated an experimental *Ku*-band MMIC analog phase shifter using the GaAs MESFET process. The insertion loss was  $3.6 \pm 1.1$  dB from 12 to 14 GHz with

more than 180° phase shift. The chip size of the experimental MMIC phase shifter was less than 3.0 mm<sup>2</sup>.

The proposed small-sized phase shifter, which does not require a 90° hybrid, is useful for the various kinds of applications from UHF frequencies to millimeter-wave frequencies, and could also be used to synchronize subharmonically injection-locked oscillators for spatial power-combining techniques [10], [11].

#### ACKNOWLEDGMENT

The authors thank Dr. M. Muraguchi, NTT Electronics Corporation, Atsugi, Kanagawa, Japan, H. Kamitsuna, NTT Photonics Laboratories, Atsugi, Kanagawa, Japan, and Dr. H. Mizuno, NTT Network Innovation Laboratories, Yokosuka, Kanagawa, Japan, for their encouragement and helpful information.

#### REFERENCES

- [1] D. M. Pozar and D. H. Schaubert, "Comparison of architectures for monolithic phased array antennas," *Microwave J.*, pp. 93–104, Mar. 1986.

- [2] R. J. Mailloux, "Phased array architecture for mm-wave active arrays," *Microwave J.*, pp. 117–104, July 1986.

- [3] J. F. McIlvenna, "Monolithic phased arrays for EHF communications terminals," *Microwave J.*, pp. 113–125, Mar. 1988.

- [4] T. Itoh, "Planar quasi-optical circuit technology," in *Proc. 20th European Microwave Conf.*, Sept. 1990, pp. 83–88.

- [5] S. K. Koul and B. Bhat, *Microwave and Millimeter Wave Phase Shifters*. Norwood, MA: Artech House, 1991, vol. II.

- [6] R. K. Gupta and W. J. Getsinger, "Quasi-lumped-element 3- and 4-port networks for MIC and MMIC applications," in *IEEE MTT-S Int. Microwave Symp. Dig.*, 1984, pp. 409–411.

- [7] H. Hayashi and M. Muraguchi, "A miniaturized MMIC analog phase shifter using two quarter-wave-length transmission lines," in *IEEE GaAs IC Symp. Dig.*, Oct. 1999, pp. 255–258.

- [8] T. Enoki, K. Yamasaki, K. Osafune, and K. Ohwada, "0.3- $\mu$ m advanced SAINT FET's having asymmetric n<sup>+</sup>-layers for ultra-high-frequency GaAs MMIC's," *IEEE Trans. Electron Devices*, vol. 35, pp. 18–24, Jan. 1988.

- [9] M. Muraguchi, T. Hirota, A. Minakawa, K. Ohwada, and T. Sugita, "Uniplanar MMIC's and their applications," *IEEE Trans. Microwave Theory Tech.*, vol. 36, pp. 1896–1901, Dec. 1988.

- [10] T. Tokumitsu, K. Kamogawa, I. Toyoda, and M. Aikawa, "A novel injection-locked oscillator MMIC with combined ultrawide-band active combiner/divider and amplifiers," *IEEE Trans. Microwave Theory Tech.*, vol. 42, pp. 2572–2578, Dec. 1994.

- [11] X. Zhang, X. Zhou, and A. S. Daryoush, "A theoretical and experimental study of the noise behavior of subharmonically injection locked local oscillators," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 895–902, May 1992.

**Hitoshi Hayashi** (M'94) received the B.Eng., M.Eng., and a Ph.D. in electronics engineering from the University of Tokyo, Tokyo, Japan, in 1990, 1992, and 2000, respectively.

In 1992, he joined NTT Radio Communication Systems Laboratories, Yokosuka, Japan. He is currently with NTT Network Innovation Laboratories, Yokosuka, Japan, where he is engaged in the development of wireless communication systems. From 2000 to 2001, he was also involved in wireless systems research at the Massachusetts Institute of Technology (MIT), Cambridge, as a Visiting Scientist.

Dr. Hayashi is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan. He was the recipient of the 1998 Young Engineer Award presented by the IEICE.

**Tadao Nakagawa** (M'91) received the B.E. and M.E. degrees in material physics and the Dr. Eng. degree in communication engineering from Osaka University, Osaka, Japan, in 1986, 1988, and 1997, respectively.

In 1988, he joined NTT Radio Communication Systems Laboratories, Yokosuka, Japan, where he was engaged in research and development on MMICs and microwave synthesizers. From 1997 to 1999, he was an Associate Manager at the STE Telecommunication Engineering Company Ltd., where he served as a Technical Consultant on wireless communications to the Seiko Epson Corporation, Nagano, Japan. Since 1999, he has been a Senior Research Engineer at NTT Network Innovation Laboratories, Yokosuka, Japan, where he is currently involved in the design of millimeter-wave transceivers and multiband transceivers.

Dr. Nakagawa is a member of the Institute of Electronics, Information and Communication Engineers (IEICE), Japan. He was the recipient of the 1995 Young Engineer Award presented by the IEICE.

**Katsuhiko Araki** received the B.E. and M.E. degrees from the Tokyo Institute of Technology, Tokyo, Japan, in 1979 and 1981, respectively.

In 1981, he joined NTT Electrical Communications Laboratories, Yokosuka, Japan, where he has been engaged in research on GaAs monolithic microwave circuits and in the development of communication satellite onboard transponders. He is currently a Senior Research Engineer, Supervisor, at NTT Network Innovation Laboratories, Yokosuka, Japan.

Mr. Araki is a member of the American Institute of Aeronautics and Astronautics (AIAA) and the Institute of Electronics, Information and Communication Engineers (IEICE), Japan. He was the recipient of the 1988 Sinohara Prize presented by the IEICE.